操作系统复习.陈向群(00-02)(概述、中断异常)

操作系统复习(00-02)

Chapter 00:课程简介

内容

- 执行一个可执行文件的时候,操作系统做了什么?

1 |

|

- 两种观点

- 用户程序:OS 功能调用、返回

- 进程调度:调度、返回

- 操作系统的主要工作

- 执行程序、个性(硬件相关)、共性、其他问题(性能、安全、健壮性等)

Chapter 01:操作系统概述

关键词

- 操作系统定义、并发性、共享性、虚拟性、随机性、SPOOLing、多道程序设计、OS/360、MULTICS、典型操作系统

思考题

- 一个应用程序的执行流程是怎样的? 涉及到哪些功能模块?

- 请问 Windows 操作系统中的设备驱动程序具体提 供了什么功能?有具体的例子吗?为什么说它不直接与硬件打交道? 可不可以理解为设备驱动程序是建立在 HAL 之上的更高层的抽象,所以是通过HAL与硬件打交道 ?

- 课件上 “UNIX操作系统”

- 文件子系统与块设备之间的 Buffer Cache 的作用是什么?

- 简要小结一下 Buffer Cache 的工作原理

- UNIX 的名字来历的猜测

- SPOOLing 技术过时了吗?

- 传统的分时系统在今天有什么意义?

内容

Windows 架构、Unix 架构、Linux 架构、Android 架构

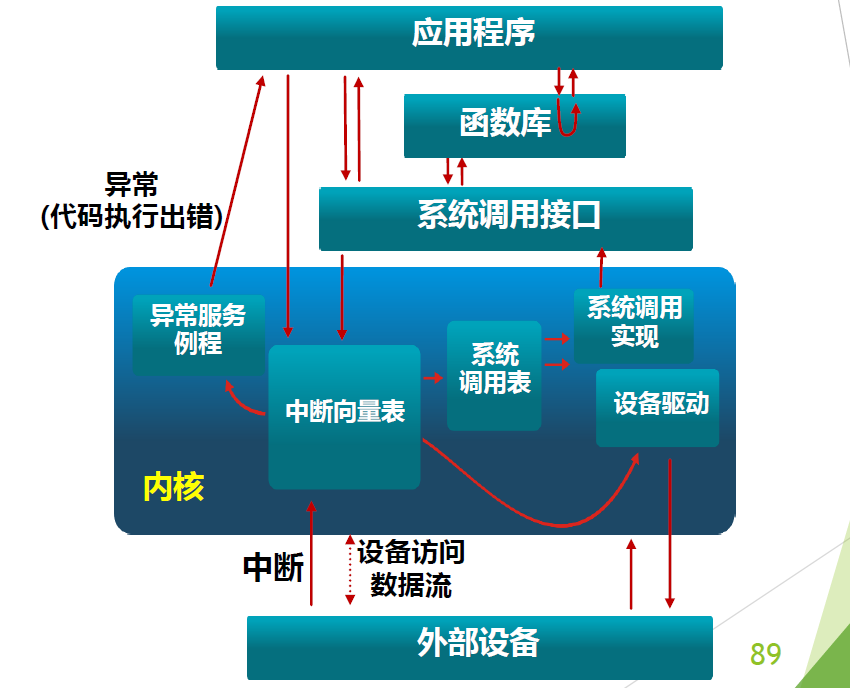

层次:应用程序、系统功能调用、操作系统、计算机硬件

操作系统是什么?

系统软件

软硬件资源管理(有效、合理)

程序执行控制,对外提供服务

用户方便使用

机器的扩展

设计与实现目标:抽象、模块化、性能、应用之间、隔离性、可靠性、节能、安全性、移动性

什么是操作系统(不同角度)?

- 作为软件来看的观点

- 资源管理的观点

- 进程的观点

- 虚机器观点(分层结构)

操作系统的特征:并发、共享、虚拟、随机

操作系统发展史

- 第1阶段 (1948 -1970 ):硬件昂贵,人工便宜

- SPOOLing(假脱机)

- 第2阶段 (1970 -1985 ):硬件便宜,人工昂贵

- 第一个分时操作系统 CTSS

- 第3阶段 (1981 -):硬件非常便宜,人工昂贵

- 第4阶段 (1981 -):分布式

- 第5阶段 (1995 -):移动计算时代

- 第6阶段 (2006 -):云计算时代

- 第7阶段 (200? -):泛在计算 / 普适计算 / 物联网

- 第1阶段 (1948 -1970 ):硬件昂贵,人工便宜

操作系统分类

- 批处理操作系统(多道)

- 分时系统

- 实时操作系统

- 硬实时系统、软实时系统

- 个人计算机操作系统

- 网络操作系统

- 分布式操作系统

- 嵌入式操作系统

操作系统的另一种分类(Tanenbaum)

- 大型机操作系统

- 服务器操作系统

- 多处理机操作系统

- 个人计算机操作系统

- 实时操作系统

- 嵌入式操作系统

- 智能卡操作系统

Chapter 02:运行环境和运行机制

关键词

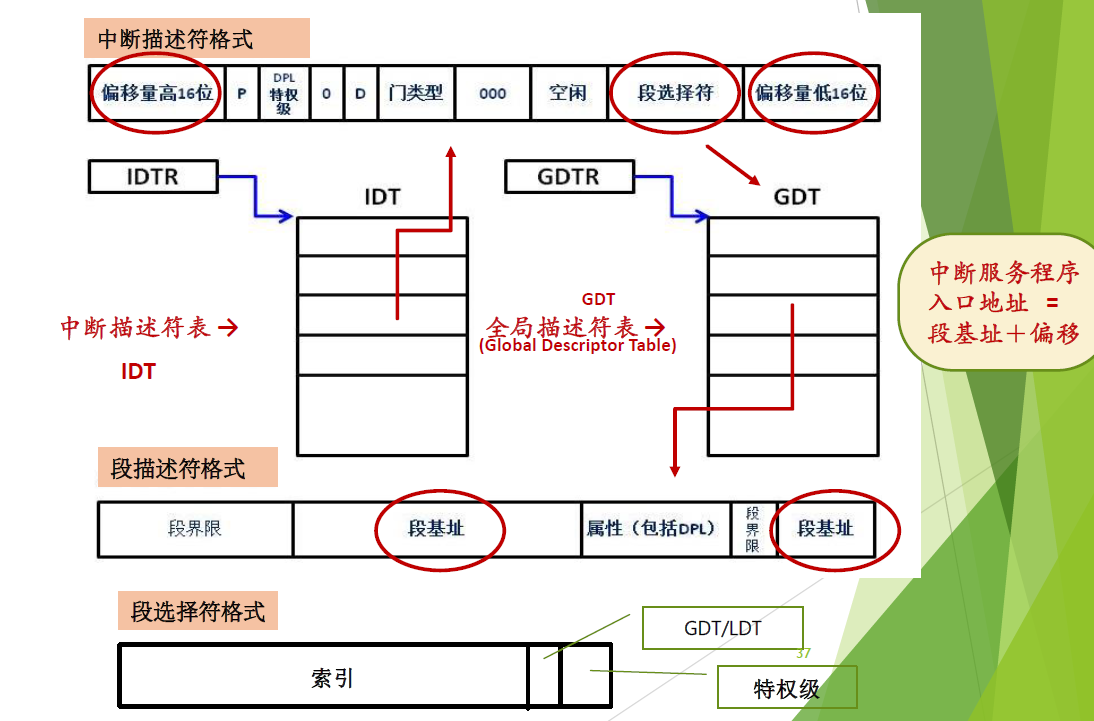

- CPU 状态 (模式 )、特权指令、非特权指令、内核态/用户态、管态/目态、R0/R3、中断与异常、中断向量表、中断描述符、系统调用、机制与策略

思考题

- 怎样理解 ”操作系统是由中断/异常/事件驱动的” 这句话?

- 中断/异常的来源有什么不同? 处理方式是一样的吗?

- 中断/异常机制中,哪些是硬件(体系结构)负责的? 哪些是软件(操作系统)负责的?

- 从中断响应(硬件)到中断处理程序(软件)执行结束,计算机系统经过了哪些流程?

- 操作系统初始化与中断/异常有哪些关联?

- 怎样理解应用程序是如何与操作系统交互的?

- 什么是软件异常? 它是如何工作的?

- X86 在 Peniuml1300 之后提供了 sysantcr/sysexit 指令,为什么?与int0x80/iret有什么不同?

- 关于基于 x86 体系结构的 Linux 的系统调用实现:

- 系统调用入口程序 system_ call() 与中断描述符表是什么关系?与系统调用表是什么关系?

- 系统调用处理结束后,处理器转去执行哪个模块?

- 系统调用与 C 函数调用的区别?

内容

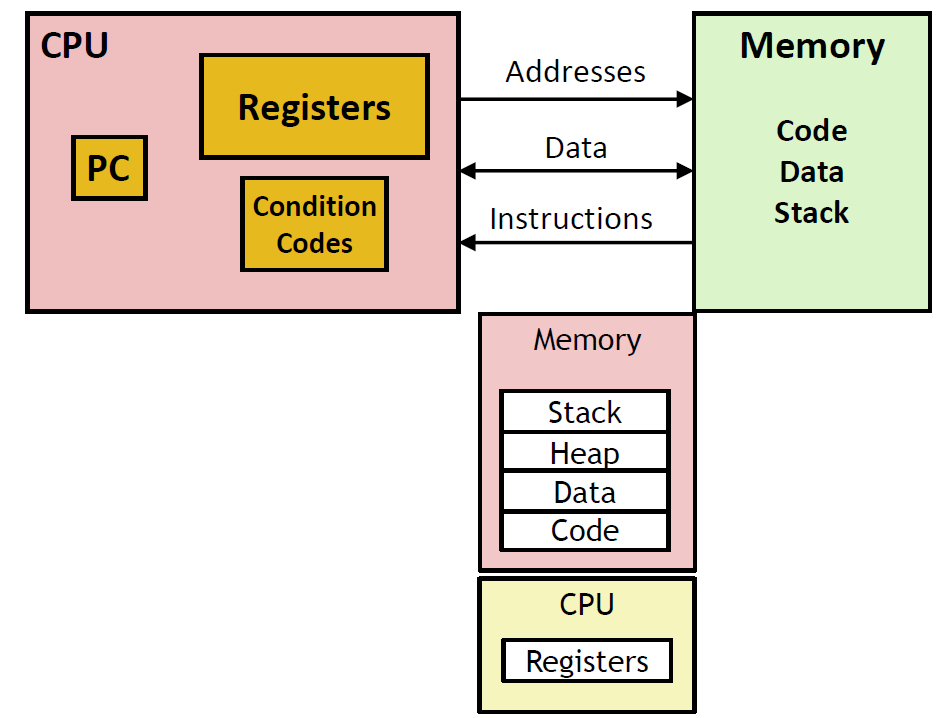

CPU

- CPU 与内存

- 两类寄存器

- 用户可见寄存器

- 数据寄存器、地址寄存器、条件码寄存器

- 控制和状态寄存器

- 程序计数器(PC)、指令寄存器(IR)、程序状态字(PSW)

- 用户可见寄存器

- 内核态与用户态

- 特权指令与非特权指令

- x86 系列处理器

- R0 \(\to\) R3:特权高 \(\to\) 低

- CPU 状态之间的切换

- 进入内核态:中断/异常/陷入机制

- 返回用户态:设置程序状态字 PSW

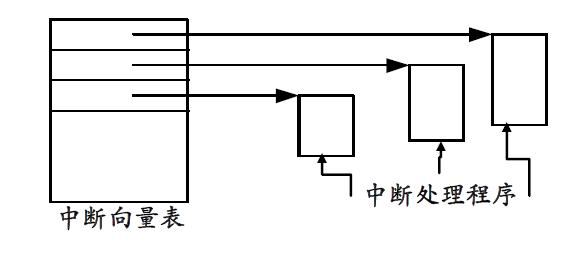

中断机制

- 中断与异常的引入原因

- 中断的引入:为了支持 CPU 和设备之间的并行操作

- 异常的引入:表示 CPU 执行指令时本身出现的问题

- 中断与异常

| 类别 | 原因 | 异步/同步 | 返回行为 |

|---|---|---|---|

| 中断 Interrupt |

来自 I/O 设备、其他硬件部件 | 异步 | 总是返回到下一条指令 |

| 陷入 Trap |

有意识安排的 | 同步 | 返回到下一条指令 |

| 故障 Fault |

可恢复的错误 | 同步 | 返回到当前指令 |

| 终止 Abort |

不可恢复的错误 | 同步 | 不会返回 |

- 中断/异常机制工作原理

- 软硬件配合

- 中断响应(中断硬件部件完成)

- 在每条指令执行周期的最后时刻扫描中断寄存器,查看是否有中断信号

- 若有中断,中断硬件将该中断触发器内容按规定编码送入 PSW 的相应位,称为中断码,通过交换中断向量引出中断处理程序

- 中断向量与中断向量表

- 中断处理程序

- 中断/异常机制中软硬件分工

- 以设备 IO 中断为例

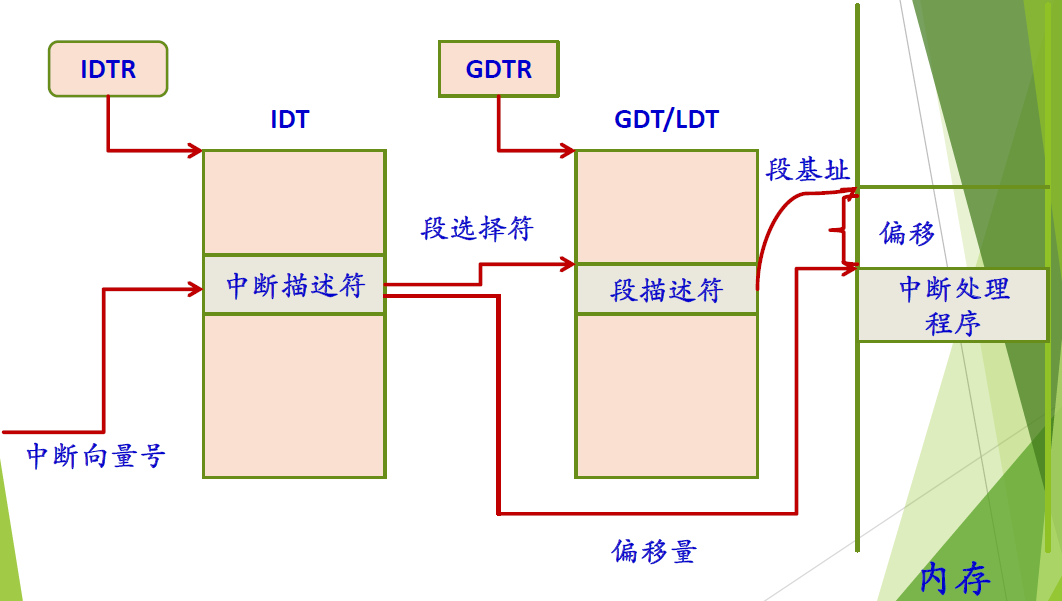

IA32 体系结构对中断的支持

- 中断控制器

- 实模式(正常情况):中断向量表

- 保护模式(刚启动):中断描述符表

- 门描述符

- IDTR 寄存器、GDTR 寄存器

- 整个流程

存储系统

- 容量、速度、成本

- 寄存器、高速缓存、主存、磁盘

- 局部性原理

I/O 访问技术

- 程序控制方式

- I/O 处理单元

- CPU 定期轮询 I/O 单元的状态,直到处理完毕

- 中断驱动方式

- 每个数据需要传输时中断 CPU

- I/O 操作与指令并行

- 直接存储器存取(DMA)方式

- 一批数据需要传输时中断 CPU

- DMA 控制

时钟

- 绝对时钟、相对时钟

- 硬件时钟、软件时钟

x86 体系结构的定时硬件

- 4 种定时硬件

- 实时时钟(RTC)

- 时间戳计数器(TSC)

- 可编程间隔定时器(PIT)

- SMP系统中的本地APIC定时器

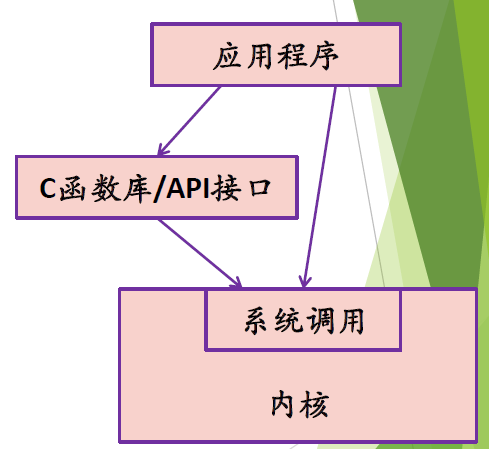

系统调用

- 系统调用、库函数、API、内核函数

- 系统调用机制的设计

- 利用中断/异常机制

- 如何实现参数传递

- 陷入指令自带参数

- 通用寄存器

- 专用堆栈区

内核的进入与退出